| Multiplication Acceleration Through Twin Precision |

| Task Migration In Mesh NOCS |

| AMBA-Advanced High Performance Bus IP Block |

| Design of On-Chip Bus with OCP Interface |

| Design of Finite Impulse Response Filter |

| Adiabatic Technique For Energy Efficient Logic Circuits Design |

| Turbo Encoder For LTE Process |

| Reconfigurable Coprocessor for Redundant Radix-4 Arithmetic |

| 4 BIT SFQ Multiplier |

| New Adaptive Weight Algorithm For Salt And Pepper Noise Removal |

| Seal Encryption On FPGA, GPU AND Multi-Core Processors |

| Lossless Implementation Of Daubechies 8-Tap Wavelet Transform |

| Design of Control Area Network Protocol |

| Asynchronous Transfer Mode Knockout Switch |

| LFSR Based Test Generator Synthesis |

| Rotation-Based Bist With Self-Feedback |

| Operation Improvement of Indoor Robot |

| Low-Power And Area-Efficient Carry Select Adder |

| Soft-Error Tolerance and Mitigation |

| Design of 16 BIT QPSK |

| Design of 64-Bit QAM |

| Custom Floating-Point Unit Generation |

| Design of JPEG Compression Standard |

| A Framework for Correction of Multi-Bit Soft Errors |

| Spurious-Power Suppression Technique for Multimedia/DSP Applications |

| Design of A Bus Bridge Between AHB and OCP |

| General Linear Feedback Shift Register |

| Design of 16 Point Radix-4 FFT Algorithm |

| Design and Implementation of Efficient Systolic Array Architecture |

| Exploitation of Narrow-Width Values |

| Design And Synthesis Of Programmable Logic Block |

| Fault Secure Encoder |

| Pipeline VLSI Architecture |

| 3-D Lifting-based Discrete Wavelet Transform |

| Shift-Register-Based Data Transposition |

| Design and Implementation of High Speed DDR SDRAM Controller |

| Design Of Parallel Multiplier Based On RADIX-2 Modified Booth Algorithm |

| Cyclic Redundancy Checker Generator |

| Multilayer AHB Bus Matrix |

| Novel Area-Efficient FPGA Architectures |

| Implementation of FFT/IFFT Blocks for OFDM |

| Behavioral Synthesis of Asynchronous Circuits |

| Implementation Of Guessing Game |

| Very Fast and Low Power Carry Select Adder Circuit |

| Short Range MIMO Communications |

| VLSI Progressive Coding for Wavelet-based Image Compression |

| Self-Immunity Technique to Improve Register File Integrity against Soft Errors |

| Universal Asynchronous Receiver Transmitter |

| Design Of 32 Bit RISC Processor |

| Implementation Of Discrete Wavelet Transform |

| Programmable Logic Block With Mixed LUT and MACROGATE |

| Design Of Reversible Finite Field Arithmetic |

| Design Of Radix-2 Butterfly processor to prevent Overflow in The Arithmetic |

| Viterbi Decoder for High Speed Applications |

| Efficient FPGA Implementation Of Convolution |

| Low Power ALU Design By Ancient Mathematics |

| Low Power Hardware Architecture for VBSME using Pixel Truncation |

| Reliable and Cost Effective Anti-collision Technique For RFID UHF Tag |

| Carry Tree Adder |

| Power Management Of MIMO Network Interfaces On Mobile Systems |

| Floating Point Multiplier |

| 8 Bit PICCO Processor |

| High-Accuracy Fixed-Width Modified Booth Multipliers |

| DDR3 Based Lookup Circuit for High Performance Network Processing |

| Performance Analysis of Integer Wavelet Transform For Image Compression |

| ASIC Design Of Complex Multiplier |

| A Processor-In-Memory Architecture For Multimedia Compression |

| Designing Efficient Online Testable Reversible Adders |

| Lightweight High-Performance Fault Detection Scheme |

| High Performance Complex Number Multiplier Using Booth-Wallace Algorithm |

| Dual Data Rate SDRAM Controller |

| FPGA-Based Architecture For Linear And Morphological Image Filtering |

| Automatic Road Extraction Using High Resolution Satellite Images |

| Low Power Flip-Flop Using Cmos Deep Submicron Technology |

| Cordic Processor for Complex DPLL |

| Digital Base Band Processor for UWB Transceiver |

| Detecting Background Setting For Dynamic Scene |

| OFDM Transmitter and Receiver Using FPGA |

| Traffic Light Controller |

| Module To Implement I2C Interface |

| Advanced Encryption System to Improvise System Speed |

| Design of Data Encryption Standard (DES) for Data Encryption |

| Low-Complexity Sequential Searcher For Robust Symbol Synchronization In OFDM Systems |

| Removal Of High Density Salt And Pepper Noise |

| Dual Stack Method |

| Quadrature Phase Shifting key Modulator Module |

| High Throughput DA-Based DCT With High Accuracy |

| Floating Point Vector Coprocessor |

| Dual Elevator Controller |

| Register For Phase Difference Based Logic |

| Building An AMBA AHB Compliant Memory Controller |

| Direct Digital Frequency Synthesizer |

| High-Speed Low-Power Viterbi Decoder Design For TCM Decoders |

| Design of Phelix Algorithm |

| Parallel Prefix Adders Using FPGAS |

| REED SOLMEN ENCODER |

| Rail-Passenger Information System |

| JPEG Image Compression |

| Triple Des Algoritm |

Is your deadline is near and your work is not done yet?

Vlsi Vhdl & Pcb Design Software

VLSI, VHDL AND PCB DESIGN A Industrial training report Submitted in Partial Fulfillment of the Requirement of the Degree of BACHELOR OF TECHNOLOGY in ELECTRONICS AND COMMUNICATION ENGINEERING by RICHA BHARTI (REG NO.20130707) Under the guidance of DR.SAGAR BOSE Training head DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING SIKKIM MANIPAL. Is a complete set of free CAD tools and portable libraries for VLSI design. It includes a VHDL compiler and simulator, logic synthesis tools, and automatic place and route tools. A complete set of portable CMOS libraries is provided, including a RAM generator, a ROM generator and a data-path compiler. Learn a EasyEDA - Free, Online PCB Design + PCB Design - Microcontroller Based Project + 1 & 2-Layer SMT PCBs. He has experience, working on various platforms & EDA Tools / Programming Softwares which includes VLSI - VHDL & Verilog Programming for Xilinx FPGAs, CPLDs using Xilinx ISE Tool / Xilinx Vivado Tool, Programming PSOC1 using.

Do not worry at all, E2Matrix VLSI & VHDLThesis Help service is here for your help. As our thesis developers are professional and also experienced, they complete your VLSI & VHDLThesis Help or Research work paper without any delay or compromise. We promised to provide you the best Thesis or Research work. There is a rising demand for chip driven products in consumer electronics, medical electronics, communication, aero-space, computers etc. More and more chip designing companies have set up their units in India eying on the Indian talents; besides many of the Indian Major IT companies have forayed in Application Specific Integrated Circuit (ASIC) design in a big way. With the design & manufacturing market (both domestic & international) expanding rapidly, there is an enhanced demand of trained professionals who will boost the technical work force in the VLSI domain.

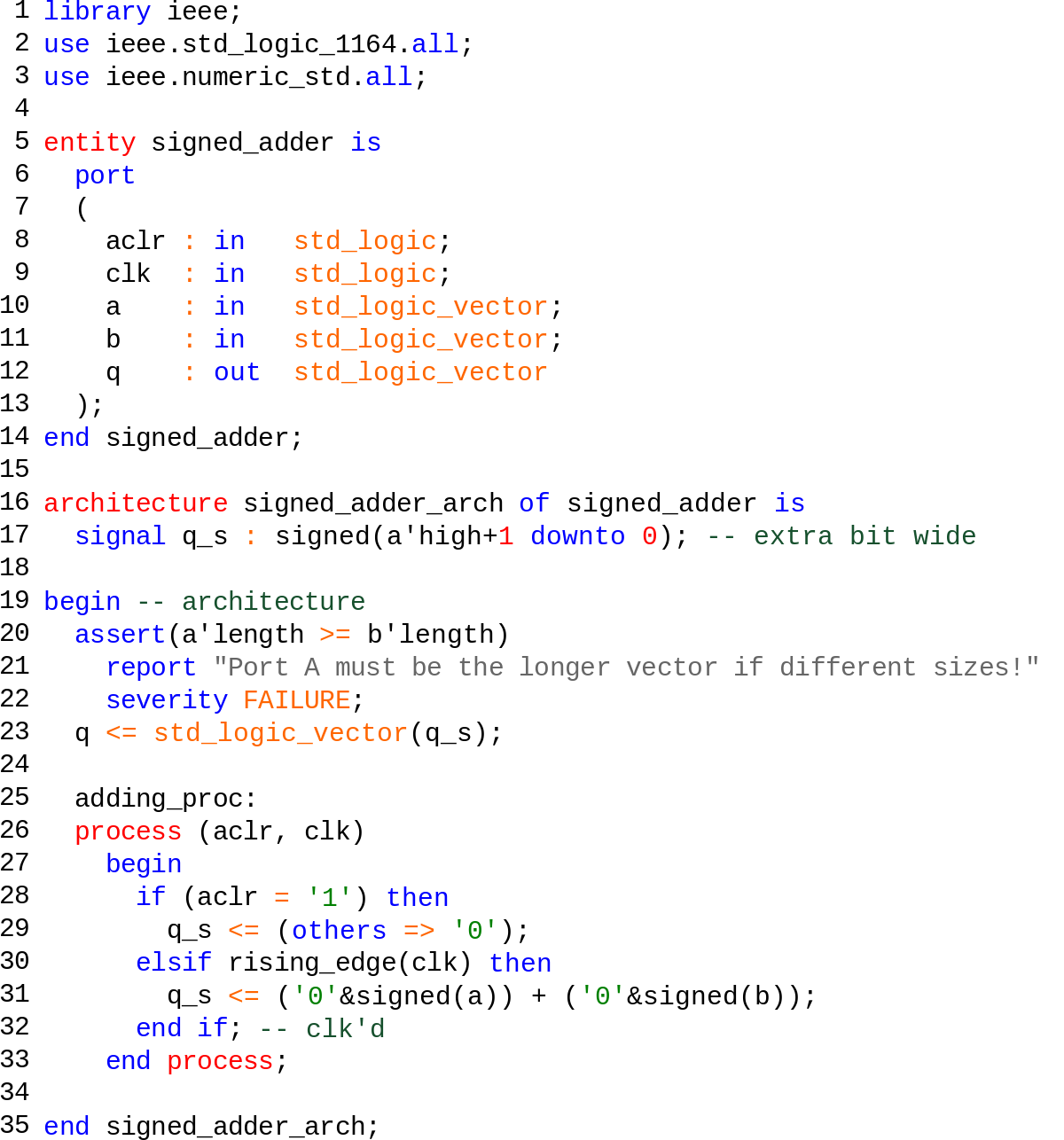

VHDL Thesis Topics:-

This Training introduces students to VHDL language, and its use in logic design. By the end of the course, students will be able to understand the basic parts of VHDL model, and its usage, build complete logic structures that can be synthesized into programmable logic device hardware.

VHDL TRAINING MODULE

VHDL Overview and Concepts

Levels of Abstraction

Entity, Architecture

Data Types and declaration

Enumerated Data Types

Relational, Logical, Arithmetic Operators

Signal and Variables, Constants

Process Statement

Concurrent Statements

When-else, With-select

Sequential Statement

If-then-else, Case

Slicing and Concatenation

Loop Statements

Delta Delay Concept

Arrays, Memory Modeling, FSM

Writing Procedures

Writing Functions

Behavioral / RTL Coding

Operator Overloading

Structural Coding

Component declarations and installations

Generate Statement

Configuration Block

Libraries, Standard packages

Local and Global Declarations

Package, Package body

Writing Test Benches

Assertion based verification

Files read and write operations

Code for complex FPGA and ASICs

Generics and Generic maps

VERILOG Thesis Topic:-

This Training introduces students to the basics and advanced version of Verilog Hardware Description Language. The course content includes Introduction to Verilog, Hierarchy, and Modelling Structures, Syntax, Lexical Conventions, Data Types, and Memories, Expressions and Simulation Mechanics, Gate Level Modelling, Behavioral and Register Transfer Level Modelling, Advanced Features, Coding Style, Debugging Verilog Models, and The Programming Language Interface.

Language introduction

Levels of abstraction

Module, Ports types and declarations

Registers and nets, Arrays

Identifiers, Parameters

Relational, Arithmetic, Logical, Bit-wise shift Operators

Writing expressions

Behavioral Modeling

Structural Coding

Continuous Assignments

Procedural Statements

Always, Initial Blocks, begin ebd, fork join

Blocking and Non-blocking statements

Operation Control Statements

If, case

Loops: while, for-loop, for-each, repeat

Combination and sequential circuit designs

Memory modeling, state machines

CMOS gate modeling

Writing Tasks

Writing Functions

Compiler directives

Conditional Compilation

System Tasks

Gate level primitives

User defined primitives

Vlsi Design Jobs

We have a best team of technical developers and professionals who specialize in creating and developing VLSI VHDL Thesis varied in nature with an assurance of on time delivery and 100% authenticated work and technical contents.

Vlsi Design Flow Ppt

Our organization helps in developing full custom VLSI VHDL Thesis and Research work. We are providing variousThesis & Research work enhancement for IEEE transactions and Journals or International Journals. Our developers are highly qualified with experience in developing various thesis, dissertations and research work.